基于DSP的运动控制器的开发

运动控制器是一种用于多种运动控制场合的上位控制单元,通常采用专业运动控制芯片或高速DSP来控制步进电机或伺服电机。运动控制器与PC机构成主从结构。PC机负责人机交互界面的管理和控制系统的实时监控工作;控制器完成运动控制的细节。运动控制器配有库函数供用户调用,这种开放的结构能够广泛应用于制造业中设备自动化的各个领域。

1 系统的构成与工作原理

1.1 系统的构成

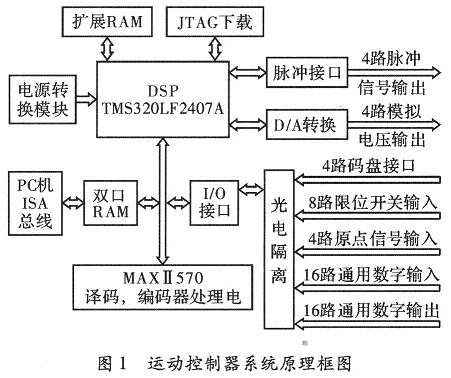

系统构成如图1所示,包括电源转换模块、DSP外围电路、脉冲输出电路、编码器信号采集和处理电路、D/A输出电路和DSP-PC机通信电路等。核心微处理器采用美国TI公司的16位定点DSP芯片TMS320LF2407A。

1.2 系统的工作原理

本系统由上位机通过双端口RAM把运动控制指令或控制参数传递给运动控制器的DSP,DSP根据采集到的PC机指令,通过位置控制和速度控制算法进行计算。然后将计算出的脉冲信号经脉冲驱动送电机驱动。

2 系统的硬件电路描述

系统硬件电路主要包括电源转换模块、DSP及外围电路、扩展存储器电路、脉冲输出电路、编码器信号采集和处理电路、D/A输出电路和DSP-PC机通信电路等。控制器板卡使用Altera公司的可编程逻辑器件MAXⅡEPM570实现数字逻辑电路设计,降低了板卡的设计尺寸,增加了板卡的可靠性和设计灵活性,它的在线编程特性可使得数字逻辑设计、硬件设计,如同软件设计一样简便。

2.1 电源转换模块

TMS320LF240A是低功耗芯片,采用3.3 V供电,本设计采用Bay Linear Inc公司生产的电源转换芯片B1117提供。

2.2 DSP接口电路

2.2.1 时钟信号

选择16MHz的有源晶振作为外部时钟信号源,从DSP的XTAL1/CLXIN脚输入,经PLL1和PLL2倍频成32 MHz信号,供DSP使用。因而TMS320LF2407A的速度可达到3 1 ns,管脚XTAL2悬空。同时,16 MHz的有源晶振也是CPLD器件MAXⅡ570的外部时钟信号源。

2.2.2 串行EEPROM接口电路

TMS320LF2407A引导ROM为用户提供两种选择:同步传输通过串行外设接口(SPI)实现;异步传输通过串行通信接口(SCI)来实现。程序代码可以加载到用户指定的位置。为了有效的引导ROM和加载,本设计将MP/MC#引脚拉低,从而使DSP工作于微控制器模式。

2.2.3 扩展RAM电路

TMS320LF2407A有1.5 kB的数据/程序RAM,544 bit双口RAM(DARAM)和2 kB的单口RAM(SARAM),但是考虑到所需的程序存储空间和数据存储空间较大,在DSP外部用一片CY62136V作为外存储器,该芯片是128 kB×16 bit的存储器,其中64 kB作为数据存储器,其余64 kB作为程序存储器空间。

2.2.4 外部I/O信号处理

通过管脚引入的硬件中断,包括轴限位中断和编码器INDEX信号中断。8个限位中断信号通过光耦隔离后接入CPLD,经CPLD相与后接入DSP中断管脚XINT1,同时这些信号与DSP的I/O口相连。当某一轴运动到限位开关处时,就会触发DSP的外部中断信号XINT1,然后DSP就可以判定哪个限位开关已经到位。光耦器件选用Toshiba公司的贴片光耦TLP121,它的平均输入驱动电流为50 mA,平均输出驱动电流为5 mA,可直接驱动TTL电路。

2.3 脉冲输出电路

每一轴的两个信号输出口PLUSE+和PLUSE-可用来输出脉冲和方向信号,这两个输出口可以由程序设定为CW/CCW双脉冲模式或脉冲方向输出模式,用户可以设定J4~J11跳线来设定脉冲为差分输出或者单端输出两种方式。

2.4 D/A转换输出电路

数模转换电路的核心芯片采用BB公司生产的12位4路电压输出的数模转换芯片DAC7625。DAC的片选信号由DSP的DS,PS,IS,STRB,R/W#,WE#,A0,A1,A2,A3,A11经过译码得到。DAC的4个通道在DSP中的I/O地址为:0000 H,0001 H,0002 H,0003 H,DAC传送寄存器地址为0004 H。

2.5 编码器电路

该编码器信号处理电路是针对增量式脉冲编码器产生的信号进行处理。为消除外部驱动器大电源的干扰,3对信号经过光耦进行隔离。利用DSP事件管理器中的正交编码脉冲(QEP)电路,对引脚上的脉冲数目和频率分别解码和计数。

2.6 DSP-PC机通信电路

这里选用美国IDT公司生产的双口RAM芯片IDT71 V321,该芯片均提供两个带有自身的控制、地址和I/O引脚的独立端口,它允许独立地读写存储器中的任何电源。IDT71V321带有片内硬件端口仲裁电路,可以允许双机同步地读或写存储器中的任何单元,同时保证数据的完整性。它的竞争原则是:(1)左右两端口的地址信号同时到达,那么谁的CE片选信号先到,慢的一方BUSY线下拉,直到快的一方访问完毕;(2)左右两端口的片选信号同时到达,那么谁的访问地址信号先到,慢的一方BUSY线下拉,直到快的一方访问完毕。将IDT71V 321的左侧信号按普通接法和DSP相接。当DSP发出读/写IDT71V321的命令时,IDT71 V321锁存左边的BUSYL信号,将此信号送到DSP。若BUSYL信号为1,则表示DSP刚才读IDT71V321不存在冲突,读/写有效;若为0,则说明DSP刚才对IDT71V 321的读/写存在冲突,本次读/写无效,DSP要重新操作。PC机对接口的寻址方式里采用L/O寻址方式,使用的控制线为IOW和IOR。

3 软件程序设计及流程

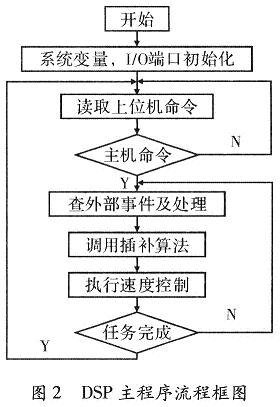

整个运动控制系统程序主要包括EEPROM引导程序和DSP主程序两部分。其中,Flash引导程序的作用是把系统程序从片外低速EEPROM传送到片外高速RAM中运行,在运动控制卡的硬件调试阶段,程序规模比较小,程序可以存放在片内的。Flash中,这样则不需要引导程序,直接在片内运行程序。系统程序主要由主程序、读写双口RAM程序、脉冲输出程序、插补程序和加减速控制程序组成。主程序调用各子程序,进行与上位机的通信、I/O、QEP、定时器及中间寄存器的初始化、设置中断标志、读取计数器的值、计算各控制量、积分平滑等功能。当发生中断时,调用相应中断程序,并修改或重置标志位。

图2所示为DSP主程序的流程图。主CPU使用硬件复位控制DSP的复位操作,DSP复位后运行片内ROM或加载到RAM中的系统主程序。DSP主程序由初始化程序、时钟循环等待中断程序组成。初始化程序完成所有变量的初始化,复位全部外设和关闭所有输出。之后进入循环和等待中断的过程,检测到主机命令之后,读取命令并根据系统需要调用相应的处理程序。命令处理完后再进入循环等待状态,命令处理程序是实现运动控制器功能的关键程序,包括运动控制的算法,速度控制、位置控制等功能的实现,还包括完成数据写入和读取等功能,同时对外部中断进行处理。当上位机给运动控制卡发送控制命令时,DSP首先读取主机发送来的轴的目标位置,根据速度控制的模式设定指令选择相应的速度控制算法,同时查询外部事件,如有事件发生,执行相应的处理程序。接着就可以送出轴的控制输出,检测各轴是否都完成运动(判断轴状态寄存器完成标志位),完成则推出命令处理程序,否则继续执行。

4 结束语

运动控制器的硬件设计需要注意:如抗干扰、外围电路的速度与DSP的实时性能匹配问题。这些问题相互影响,要确定一个正确的电路结构和合理的PCB布线,需要大量的实际经验,因此在电路结构方面仍有待改进,使之更适应稳定、高速的控制要求。对控制软件的改进主要包括以下两方面:

(1)完成上位机上接口函数、运动控制函数库和上层调试环境的设计、编写NURBS数学处理程序,在运动控制器内部实现不同的插补算法,建立运动控制器的操作平台和完善的人机交互功能,使得运动控制器具有更强大的控制性能和更容易编程;

(2)对伺服电机的控制只提供了硬件上的支持,在软件上需要对光电编码器的反馈信号进行分析,计算出与给定位置的误差,再通过软件PID算法调节器获得位置控制量来控制伺服系统。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。